Since Conformal has all the information of library cells ie. Encounter Conformal ASIC EC CONFRML52 USR1 Encounter Test ET 304 ISR.

Power Aware Verification Methodology

Cadence customers can learn more in a Rapid Adoption Kit RAK titled Conformal Low Power and RTL Compiler.

. Power and Ground nets are very often defined as type signal. Another requirement is that your standard cell power connection must be described as an inherited connection. 0000010663 00000 n Conformal ECO Designer Conformal Low Power As designs continue to get more complicated in order to meet aggressive requirements for power performance area and time to market the formal verification of the designs continues to be a staple and must-have signoff metric to ensure silicon success.

The basic flow is to input both an RTL netlist and a synthesized netlist and then have Conformal check whether both netlists are equal. If playback doesnt begin shortly try restarting your device. You may have even worked with them in the past.

Cadence Conformal Low Power has an intuitive debug infrastructure that enables fast and accurate static low-power verification with full-chip capacity and ease of use. Think of it as an LVS for Verilog. Transition with set sys mode lec.

Models have been loaded can compare. Automatically tries to map key points. Encounter Conformal Low Power is available in XL and GXL offerings.

And its personal with Clay and Bruce. Setup Mode Mapping Mode and Compare Mode. Conformal coatings protect electronic printed circuit board s from moisture and contaminants preventing short circuits and corrosion of conductors and solder joints.

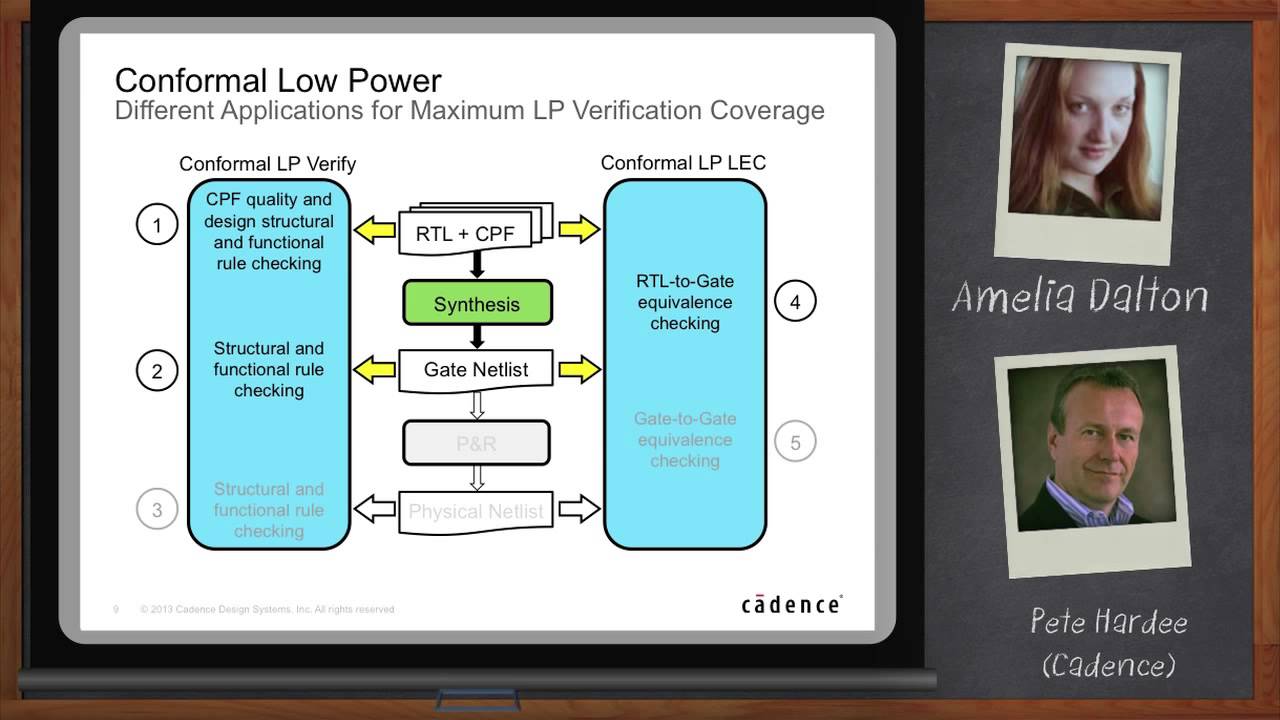

AON-cells retention-cells power-switches iso-cellslevel-shifters etc thus it would be more benefical. Any bug found at this stage leads to an ECO which can be expensive to correct in time effort and silicon. It combines proven equivalence checking structural and functional checks and formal techniques to enable full-chip low-power optimi-zation and verification.

And empirically demonstrate guaranteed false negative rate and low false detection positive rate using very. It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use. It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use.

Team FED. As designs continue to get more complicated in order to meet aggressive requirements for power performance area and time to market the formal verification of the designs continues to be a staple and must-have signoff metric to ensure silicon success. A Tutorial on Conformal Prediction Glenn Shafer GSHAFERRUTGERSEDU Department of Accounting and Information Systems Rutgers Business School 180 University Avenue Newark NJ 07102 USA Vladimir Vovk VOVKCSRHULACUK Computer Learning Research Centre Department of Computer Science Royal Holloway University of London Egham Surrey TW20.

Join this quarterly webinar to learn some essential debug steps that will enable you to identify root cause low-power issues with minimal effort. Low Power Verification for Advanced Users. Logical Equivalence Check flow diagram.

LEC comprises of three steps as shown below. 1 Check to make sure you have the following files with the correct size in. Formal verification-driven equivalence low-power and ECO solutions.

Also quality and consistency of outcome is operator-dependent so variations are. Conformal Verify CPF Flow Graphical Interface Introduction. Encounter Conformal Low Power address these challenges.

Benefits Minimizes silicon re-spin risk by. Conformal coatings are traditionally applied by dipping spraying or simple flow coating and increasingly by select coating or robotic dispensing. We are considering Conformal tool as a reference for the purpose of explaining the importance of LEC.

If you didnt know Conformals very own AE team put together some cool training materials for their customers based on large demand to help both new and intermediate users. Low Power Logic Implementation and Verification Using CPF Still no need to specify power or ground nets at this design stage Minimal set of CPF commands for designers to use Logic synthesis tools to synthesize isolation level shifter and state retention logic to perform power domain aware logic synthesis to perform power mode aware DVFS synthesis Test. Cadence Conformal Low Power 支持在设计环境中创建和验证功耗意图.

Before you start make sure that the CPF created is verified for correctness using the Cadence Conformal Low Power product. This low power reference flow solution has been validated as being compatible with IBM and Chartered for their. Low-Power IP Design Verification Engineer for AMD at santa clara California.

Encounter Conformal Low Power enables designers to create power intent then verify and debug multimillion-gate designs optimized for low power without simulating test vectors. Conformal can read liberty files but the relevant lowpower special cells are not recognised until those are specially specified with define_ cpf command. Common application methods for conformal coatings.

The basic flow is to input both an RTL netlist and a synthesized netlist and then have Conformal check whether both netlists are equal. Conformal LEC Logic Equivalence Checker Basic Training Manual Verplex Cadence Conformal Tutorial. This can be time-consuming and may need to be masked.

To run the tutorial install the tarkit and execute the following steps. Here is the course to take you a little more in-depth into the concepts and techniques used for such verification. Cadence Conformal.

Manual spraying - For low volume production when capital equipment is not available conformal coating can be applied by an aerosol can or handheld spray gun. This tutorial provides a quick getting-strated guide to Cadence Conformal logic equivalence checking. There are various EDA tools for performing LEC such as Synopsys Formality and Cadence Conformal.

This tutorial provides a quick getting-strated guide to Cadence Conformal logic equivalence checking. A tutorial on conformal prediction can be. Eco must be played on a server.

The kit includes overviews tutorials with demo design instructions are provided on how to set up uthe ser environment and provides introductions for the advanced features of Conformal Low Power --. Conformal tutorial to run it. Verification of the power intent of the design is captured and verified by Conformal Low Power CLP which requires a netlist even better a power connected netlist.

Conformal Low Power Verify CPF Rule Filtering. Conformal low power enables designers to create power intent then verify and debug multi-million-gate designs without simulating test vectors.

Low Power Design And Verification

Low Power Design Techniques Design Methodology And Tools Edn

Cadence Low Power Solution Rtl To Gdsii Low Power Design Cadence Youtube

Low Power Design And Verification

Low Power Design And Verification

Low Power Design Techniques Design Methodology And Tools Edn

Low Power Design Techniques Design Methodology And Tools Edn

Low Power Design Techniques Design Methodology And Tools Edn

0 comments

Post a Comment